Intel has recently announced a new range of FPGA’s known as Intel Agilex which are aimed at data-centric applications. The new product family has been designed to solve challenges across embedded, network and datacentre markets.

‘The race to solve data-centric problems requires agile and flexible solutions which can move store and process data efficiently. Intel Agilex FPGAs deliver customised connectivity and acceleration while delivering much needed improvements in performance and power1, 2 for diverse workloads,’ said Dan McNamara, Intel senior vice president, Programmable Solutions Group.

Customers need solutions that can aggregate and process increasing amounts of data traffic to enable transformative applications in the emerging, data-driven industries like edge computing, networking and cloud. Whether it’s through edge analytics for low-latency processing, virtualised network functions to improve performance or datacentre acceleration for greater efficiency, FPGAs are built to deliver customised solutions for applications from the edge to the cloud.

Advances in artificial intelligence (AI) analytics at the edge, network and the cloud are compelling hardware systems to cope with evolving standards, support varying AI workloads, and integrate multiple functions. Intel Agilex FPGAs provide the flexibility and agility required to meet these challenges and deliver gains in performance and power1,2.

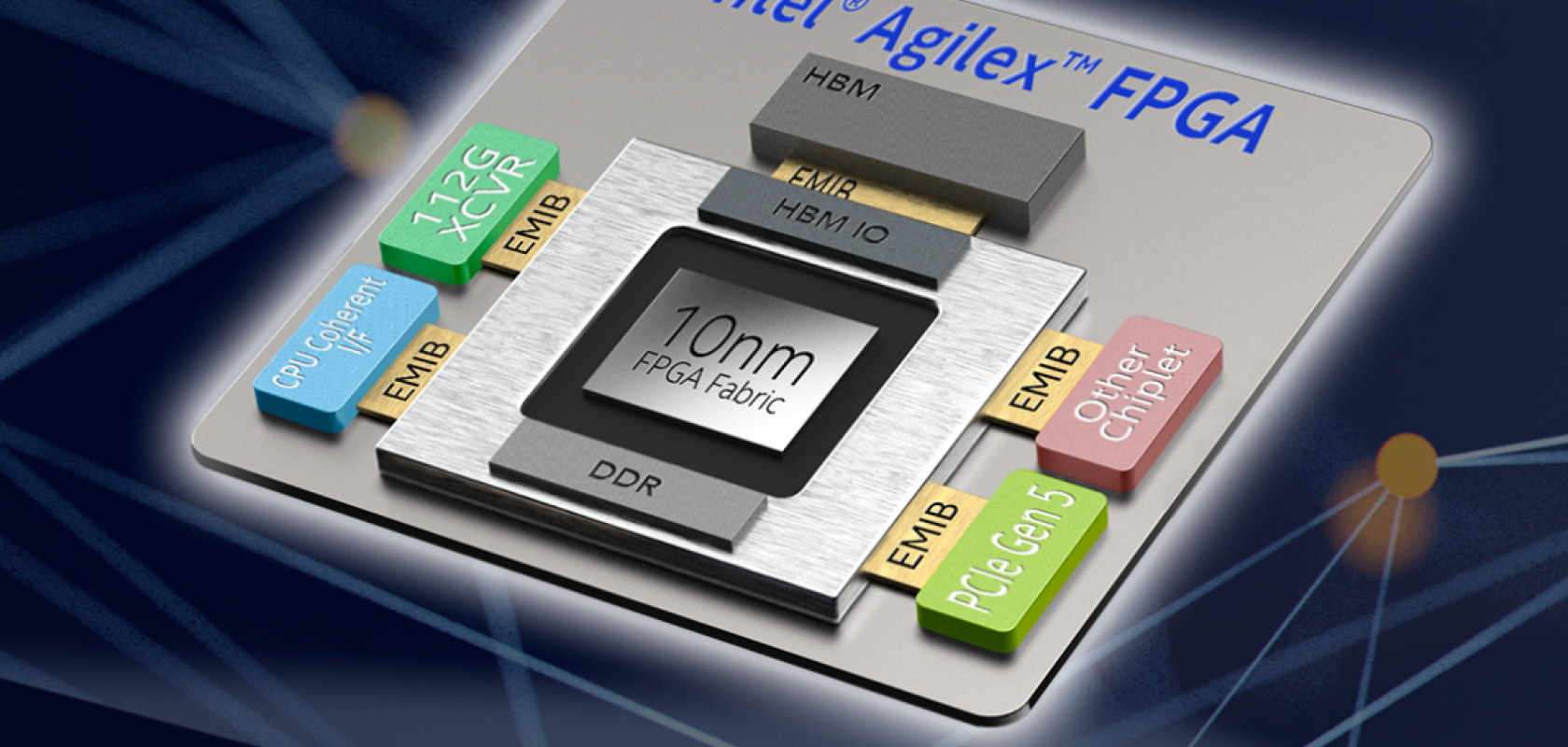

The Intel Agilex family combines FPGA fabric built on Intel’s 10nm process with innovative heterogeneous 3D SiP technology. This provides the capability to integrate analog, memory, custom computing, custom I/O, and Intel eASIC device tiles into a single package with the FPGA fabric. Intel delivers a custom logic continuum with reusable IPs through a migration path from FPGA to structured ASIC. One API provides a software-friendly heterogeneous programming environment, enabling software developers to easily access the benefits of FPGA for acceleration.

The Intel Agilex FPGA provides new capabilities to help accelerate the solutions of tomorrow. These innovations include:

- Compute Express Link: Industry’s first FPGA to support Compute Express Link, a cache and memory coherent interconnect to future Intel Xeon Scalable processors.

- 2nd Generation HyperFlex Architecture: Up to 40 percent higher performance, or up to 40 percent lower total power2 compared with Intel Stratix 10 FPGAs.1

- DSP Innovation: Only FPGA supporting hardened BFLOAT16 and up to 40 teraflops of digital signal processor (DSP) performance (FP16).3

- Peripheral component interconnect express (PCIe) Gen 5: Higher bandwidth compared with PCIe Gen 4.

- Transceiver Data Rates: Support up to 112 Gbps data rates.

- Advanced memory support: DDR5, HBM, Intel Optane DC persistent memory support.

Further details on Intel Agilex performance, power, and software support numbers:

1 Up to 40 per cent higher performance compared to Intel Stratix 10 FPGAs

Derived from benchmarking an example design suite comparing maximum clock speed (Fmax) achieved in Intel Stratix 10 devices with the Fmax achieved in Intel Agilex devices, using Intel Quartus Prime Software. On average, designs running in the fastest speed grade of Intel Agilex FPGAs achieve a 40 per cent improvement in Fmax compared to the same designs running in the most popular speed grade of Stratix 10 devices (-2 speed grade), tested February 2019.

2 Up to 40 per cent lower total power compared to Intel Stratix 10 FPGAs

Derived from benchmarking an example design suite comparing total power estimates of each design running in Intel Stratix 10 FPGAs compared to the total power consumed by the same design running in Intel Agilex FPGAs. Power estimates of Intel Stratix 10 FPGA designs are obtained from Intel Stratix 10 Early Power Estimator; power estimates for Intel Agilex FPGA designs are obtained using internal Intel analysis and architecture simulation and modeling, tested February 2019.

3 Up to 40 TFLOPs of DSP Performance (FP16 Configuration)

Each Intel Agilex DSP block can perform two FP16 floating-point operations (FLOPs) per clock cycle. Total FLOPs for FP16 configuration is derived by multiplying 2x the maximum number of DSP blocks to be offered in a single Intel Agilex FPGA by the maximum clock frequency that will be specified for that block.